| cyclone 5 music synthesizer |

| Intro Page |

| History of PLD Synths |

| FPGA Synthesizer |

| PLD Synthesizer |

| Music Tool Chain |

| Contact Me |

| Guest Book |

| imprint |

|

Let' beep! A Music Synthesizer with Cyclone V FPGA

This page describes my intended FPGA music synthesizer. It is a improved reproduction of my PLD synthesizer and mostly rebuilt. A PCB Design was planned but not realized completely. For the moment i am going with a demonstration bord of ALTERA.

Block Diagram of the Cyclone 5 FPGA Synthesizer with MIDI input, GUI and AC97 audio jacks

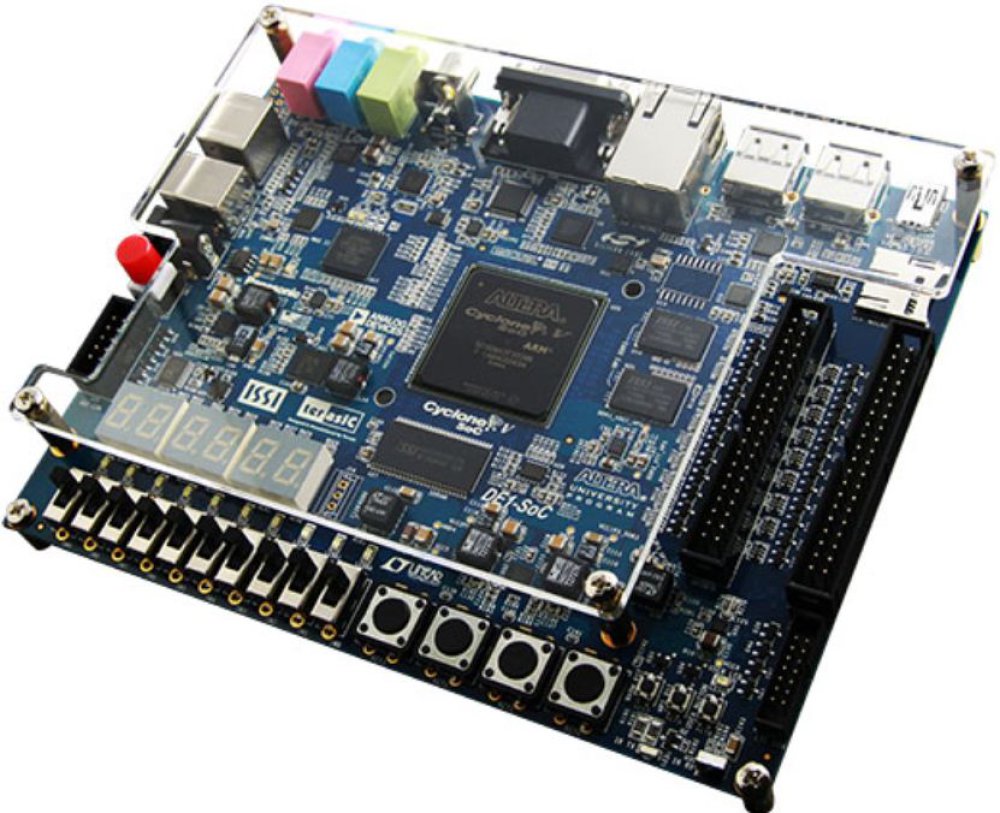

Terasic Cyclone 5 SOC PCB

The DE1-SoC Development Kit presents a robust hardware design platform built around the Altera System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. Users can now leverage the power of tremendous re-configurability paired with a high-performance, low-power processor system. Altera’s SoC integrates an ARM-based hard processor system (HPS) consisting of processor, peripherals and memory interfaces tied seamlessly with the FPGA fabric using a high-bandwidth interconnect backbone. The DE1-SoC development board includes hardware such as high-speed DDR3 memory, video and audio capabilities, Ethernet networking, and much more.

The structure is almost the same as it used to be in the first PLD-synth with some extensions:

- a tremolo and finetune had been added to the synthesis frequency (idea taken from Scott Gravenhorst's synthesizers)

- a wave shaping is performed in that way, that the waves are mixed together rather than switched (idea taken from Jürgen Schuhmacher's synthesizers)

- a sawtooth has been added (done in almost all analog synths)

- extended ADSR with velocity control is used (own idea)

- The ADSR module is now more complex and moved to a own section (ADSR behavior inspired by Chris Strellis FPGA Synth)

- 2 voices used per key note

- module is multiplexed to get 64 voices for full keyboard

- octave setting was removed because not required anymore

- sine wave removed because hard to realize, a tribute to the number of voices

The Voice has been cut into two parts to let them run individually parallel. This makes it possible to get along with only 16 clock cylces each. Internally all is parallel. The voices are multiplexed. The parameters are loaded in 2 CCs only from block ram in parallel mode and afterwards stored again. So the calculating architecture is used for >128 voices at 48kHz making 98,2 MHz. Using a 100 MHz Quarz Oscillator, the FPGA can do all the work which is necessary. From the 2x64 voices, 61 can be used with a standard keyboard.

The next move was to speed up the design to run on 140 MHz, so 3 voices per Key can played the same time.

Unlike the most synthesizers, SINE SQUARE and SAWTOOTH are not used alternately but simultaneously and mixed together. Credids to Jürgen Schuhmacher for this idea. This saves a lot of space in the FPGA but gives the chance to generate various wave shapes with even and odd hamonic control. The Module requires 16 clock cycles to operate fully, because this is the longest path in the design including flipflops for registering and time for loading and saving to RAM registers. See the PLD Synth for a precise explanation of the function.

The complete ADSR processor has been joined with the loudness control of the channel and the tremolo function. Also the compressor section is put into this module. Calculation times of the DSP and the SYNTH modul do match for easier operation. Unlike the PLD synthesizer, this new version has a velocity curve included to be manipulated by the user in real time.

credits

Thanks to the following pages and authors:

https://github.com/wware/fpga-synth

http://www.strellis.com/fpga.shtml

Verantwortlich für den Inhalt dieser Seite ist ausschließlich der

Autor dieser Homepage, kontaktierbar über dieses Formular!